アナログ集積回路の高性能化およびその応用を通じ、人にやさしい社会づくりに貢献します。

大阪工業大学 工学部 電気電子システム工学科

研究の背景

半導体集積回路の技術革新は,20世紀後半から今日に至るまでの我々の生活に劇的な変化をもたらしました。今や我々の身の回りに普通にある携帯電話やゲーム機などには,複雑な信号処理を一瞬のうちに行う最先端のLSI

(大規模集積回路) が搭載されています。これからもハードウェア,ソフトウェアの設計・開発はとどまることなく進歩していくことでしょう。

高周波集積システム研究室では,集積回路設計の基礎となるトランジスタを用いた回路の動作原理の理解をはじめ,様々な高周波アナログ回路の設計・製作を通じて,身をもって設計技術の習得を図ります。

さらに,近年の超微細化トランジスタを用いた回路設計で問題となっている,トランジスタの特性ばらつきやノイズ耐性の劣化に対して,原因解析や新規回路の

提案といった様々なアプローチを図り,将来の回路技術の進歩に寄与していきたいと考えています。

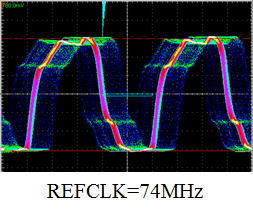

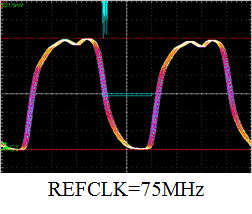

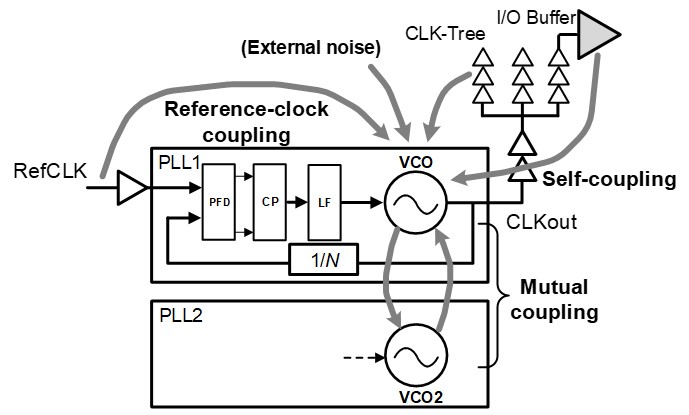

発振器および位相同期回路の干渉ノイズの影響

私たちの研究室では、半導体集積回路を設計し、外部に委託して(VDEC試作サービス)ICチップを試作しています。下の波形は、そのチップに搭載されているPLL回路を動作環境を変えて測定したものです。同じ環境(電源電圧、温度、周辺回路の状況)にも関わらず、動作周波数をほんの少し変化させただけで、出力ジッタ(=時間方向の信号の変動)が大きく変わる場合があります。

これに対する処方箋は様々で、多くの場合とりあえず思いつくことを施してみて、そのうちに直る場合もあります。往々にして、★実績のある回路は可能な限り変更しない、★とりあえずノイズ源から遠くに離す、これしかない!と思う人も多いでしょう。ノイズ問題さえなければ、アナログ回路の設計は本当に楽なのに...と感じます。

私たちの研究室は、統一した考え方が難しいこのノイズ問題に対して、発振器の干渉ノイズへの応答という観点で研究しています。工学系ではありますが、何故このような現象が生じるのか、どのようにモデル化できるかなど考えるのは、推理小説を読み解く面白さと共通するものがあります。

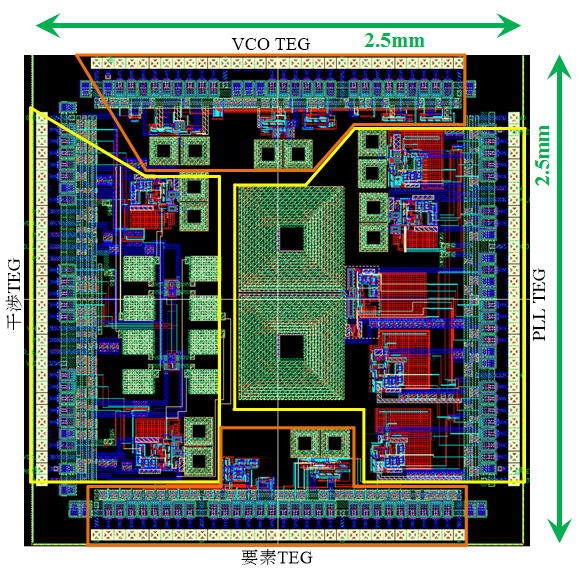

高周波低ノイズPLL回路の設計と製作

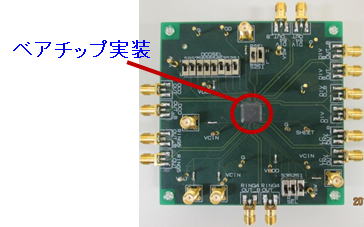

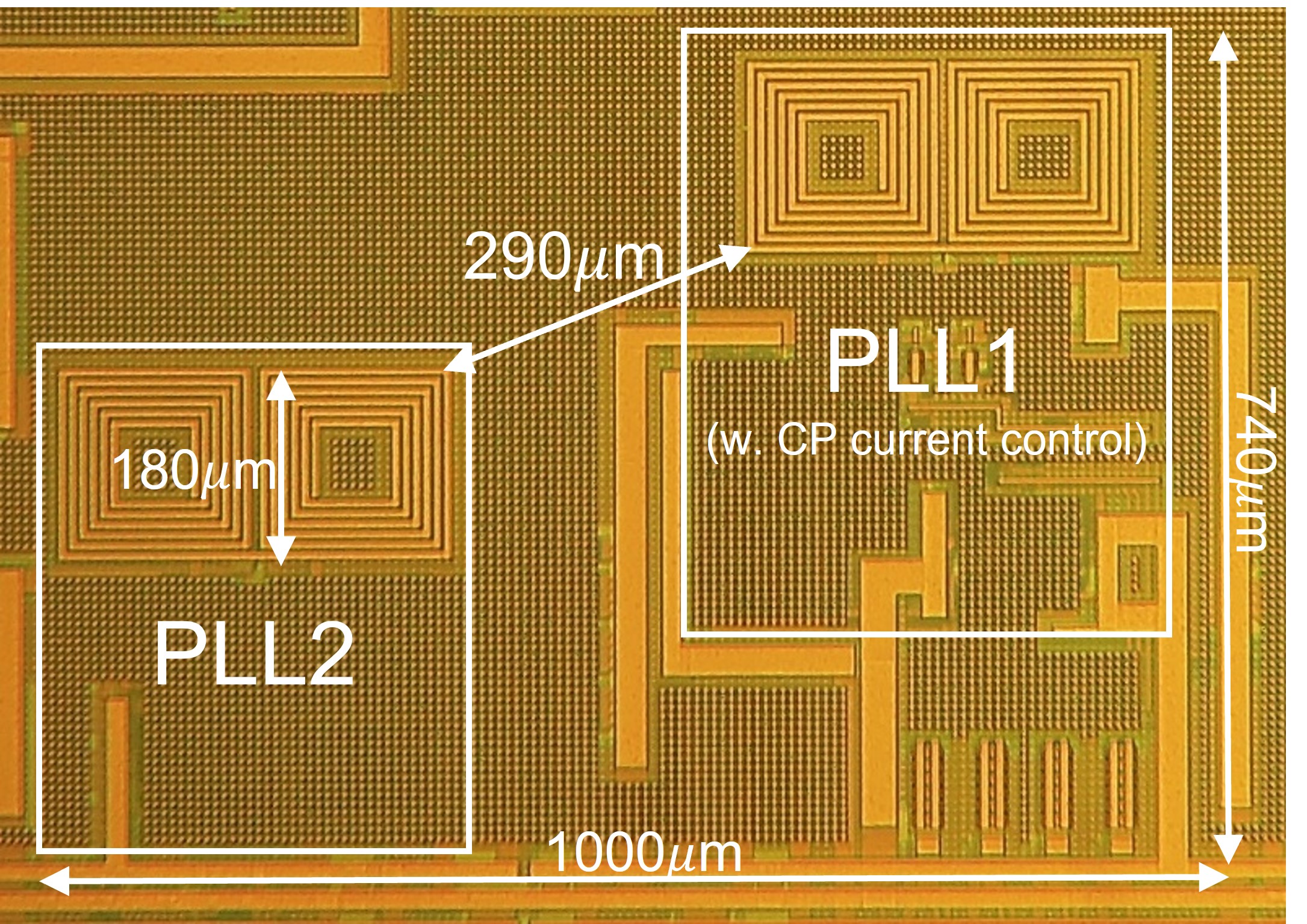

ノイズ問題の研究と並行して、半導体集積回路の設計をとおしていろんな回路のアイデアを実際のIC製作につなげていきます。これまでにローム 0.18μmCMOSプロセスを使って数回試作を行いました。

またGHz帯データ伝送を可能にするために、専用基板および基板に直接チップを実装するベアチップ実装を行い、超GHzでのデバイス測定を行っています。

発振器のカップリングの応用とその高性能化についての研究

現在、本研究室の研究により位相同期回路の発振器の相互干渉やカップリングについて、少しずつ明らかになってきています。ノイズの強度と回路への影響を定量的につかんだり、予測したりすることがだんだんできるようになってきました。

今は、電磁カップリングのメカニズム検証用ICや、カップリングを積極的に活用して性能向上を進める試みを行っています。今後、自動的にノイズをキャンセルする技術確立に向けて研究を進めていきます。

高周波集積システム研究室の研究活動リストはここをクリック。